## EECS 312: Digital Integrated Circuits Midterm Exam

24 November 2009

Robert Dick

Show your work. Derivations are required for credit; end results are insufficient. Closed book. No electronic mental aids. One side of one 8.5×11 inch page of notes may be used during the exam. permitted.

Honor Pledge: I have neither given nor received aid in this exam.

Signature:

## 1 Qualitative questions

1. (10 pts.) What is the optimal number of inverter stages to use between the fixed-capacitance inverter and the load in the following circuit? Using no more than three sentences, explain your answer.

2. (10 pts.) List two advantages of ratioed logic, and two disadvantages of ratioed logic.

advantages: (1) Less area due to fewer transitions

and (2) Less driven capositione. Disadvantages: (1) High static power consumption When output low and institly to produce OV output 3. (10 pts.) For each of the following types of load, indicate the scales (e.g., gate-level) at which the type of load will have a significant impact on circuit behavior:

(a) The Sistive,

All levels above gate level. Transistor R is

important at all levels, but we are considering loss

(b) Capacitive, and here.

All the way down to transistor level. (a) Resistive,

(c) Inductive.

Parhase - PCB level. Maybe a problem for very long global inter-4. (10 pts.) What trend has caused the importance of inter-wire coupling capacitance, relative

to substrate coupling capacitance, to increase?

Tureasing interconnect aspect ratio.

## 2 Quantitative questions

5. (10 pts.) Draw the schematic for a non-inverting Schmitt trigger buffer composed entirely of NMOSFETS and PMOSFETS, i.e., if you need a resistor, use a MOSFET instead. You needn't specify precise transistor sizes, but may specify that individual transistors are wide (use W), medium (use M), or narrow (use N). It is understood that PMOSFETs will have twice the width of NMOSFETS with the same label. When the output of your design changes, this should have little impact on the previous gate, i.e., the gate driving your design, so be sure to have a high resistance at the input of your gate.

$$q = \sum_{v} f(a)$$

$\Rightarrow q = \sum_{v} f(a)$   $f(a)$   $f(a)$

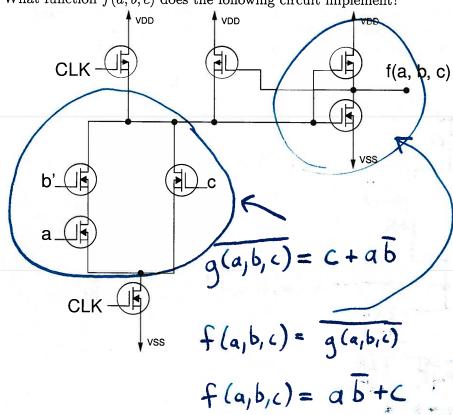

6. (10 pts.) What function f(a, b, c) does the following circuit implement?

7. (10 pts.) Implement the following function using the minimal number of transistors. The output of your implementation should have full output range, from  $V_{SS}$  to  $V_{DD}$ . However, it needn't be particularly fast. You may use literals as direct inputs.

Most or full credit was given for same designs w. 48 transistors. However, 2 worted to see how for this could be pushed.

Marrows:

The f(a,b,c)

Mide. Lie f(a,b,c)

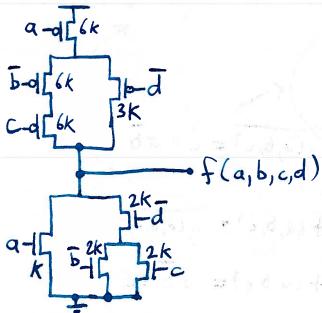

8. (10 pts.) Implement the following function as a single logic gate. Indicate the widths of all gates in terms of k, the minimal gate width. Size the transistors to achieve the same worst-case resistance as a balanced, minimal width inverter (i.e., an inverter with a k-wide NMOSFET and a 2k-wide PMOSFET).

$$f(a,b,c,d) = \overline{a}(b\overline{c}+d)$$

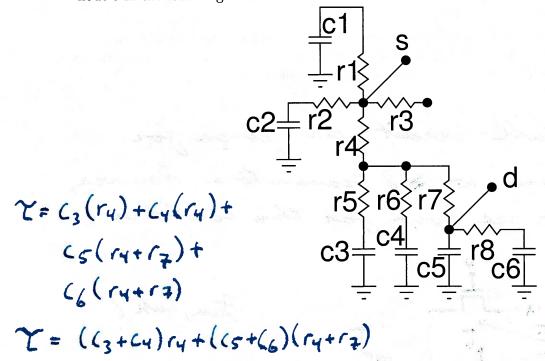

9. (10 pts.) What is the Elmore delay time constant for the response at node d to a change at node s in the following circuit?